Outperformed on performance, split the volume? Samsung Electronics’ ‘loss-leader’ strategy revealed in HBM4

Input

Modified

“First mass production of HBM4” restores confidence in technology

Commodity DRAM selected as the profit engine

Limiting volume in high-priced segments to contain losses

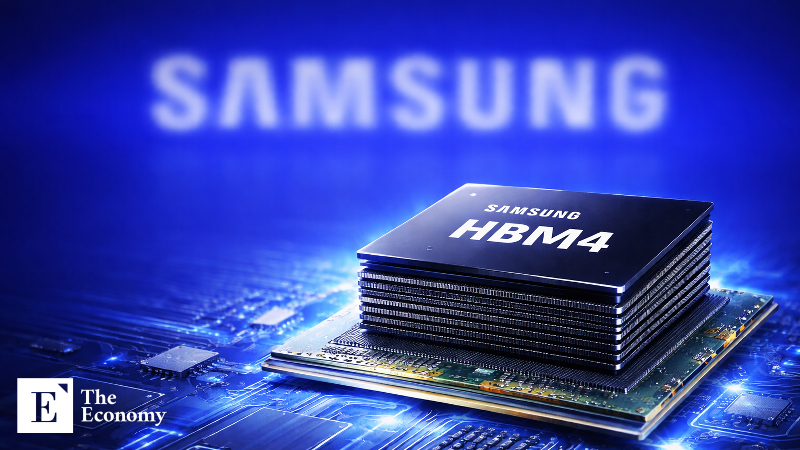

NVIDIA’s allocation of initial volumes of high-bandwidth memory (HBM)4—set to be used in its next-generation artificial intelligence (AI) accelerators—among Samsung Electronics, SK hynix, and Micron has revealed a new configuration in the HBM market. Samsung Electronics became the first in the industry to mass-produce HBM4, demonstrating performance and technological capability, but its initial volume share remained in the mid-20% range. The decision is interpreted as a comprehensive assessment of production process maturity, yields, and supply capacity. This trajectory has led to broader discussion over the role Samsung intends HBM4 to play going forward.

HBM3E rout reversed

According to the semiconductor industry, NVIDIA provisionally allocated HBM4 volumes to Samsung Electronics, SK hynix, and Micron in December last year. Given that HBM fabrication typically takes more than six months, the judgment was that volumes must be distributed in advance to enable stable production in the second half of the year of new AI accelerators, “Vera Rubin,” equipped with HBM4. Based on current understanding, provisional shares are in the mid-50% range for SK hynix, the mid-20% range for Samsung Electronics, and around 20% for Micron. The outcome reflects a broad consideration of recent transaction relationships, each company’s production capacity, and the likelihood of passing quality tests.

Some in the market expressed puzzlement at Samsung Electronics’ HBM4 share. Despite successfully taking the technological lead by being first to mass-produce and ship HBM4, its share remains relatively low compared with competitors. In fact, Samsung Electronics’ HBM4 reportedly operates at 11.7 gigabits per second (Gbps), well above NVIDIA’s requirement of 10Gbps, and was the first to pass quality testing. Even so, with SK hynix securing a dominant mid-50% share, observers believe factors beyond simple performance comparisons were at play.

Samsung Electronics applied a 4-nanometer (nm) foundry process to the base die, a key HBM4 component, and used 10nm sixth-generation (1c) DRAM for the core die. Compared with competitors that largely apply 12nm foundry processes and 10nm fifth-generation (1b) DRAM, this represents a combination more than one generation ahead. While this secured a performance edge, it inevitably brought cost pressure. In an industry where higher shares of advanced processes simultaneously raise difficulty and costs, bearing large volumes at an early stage is seen as a heavy burden.

Yield and production capacity are also cited as constraints on volume expansion. Although yields for Samsung’s HBM4-dedicated 1c DRAM are said to have improved rapidly, they are still widely viewed as trailing competitors’ more mature 1b DRAM. In addition, production capacity for 1c DRAM—the base material for HBM4—stands at roughly 70,000 wafers per month, about 10% of Samsung Electronics’ total DRAM capacity. While capacity is expected to expand to around 190,000 wafers next year through the expansion of the Pyeongtaek Line 4 plant, the industry consensus is that sharply increasing supply in the short term remains difficult.

That said, several factors support expectations for future volume increases. Most notably, Micron’s potential exit from the supply chain has been raised. In a recent report, market research firm SemiAnalysis lowered Micron’s HBM4 share in NVIDIA’s Vera Rubin to 0%. SemiAnalysis noted that “there are no signs that NVIDIA is placing HBM4 orders with Micron at present,” adding that “Micron is struggling to meet NVIDIA’s requirements, including data transfer speeds.” Such circumstances have fueled expectations that volumes allocated to Samsung Electronics could increase.

Maximizing profits with mass-supply-capable product lines

Viewed in this context, Samsung Electronics’ HBM4 performance appears focused more on restoring “technology trust” than on volume competition. After failing to demonstrate competitiveness in HBM3 and HBM3E and seeing market confidence shaken, Samsung reversed sentiment by achieving top performance and first mass production with HBM4. While smaller volumes may seem like a short-term weakness, the company has clearly set a benchmark in performance and technology, marking a new phase in its HBM strategy.

At the same time, Samsung Electronics adopted a kind of “dual strategy” by designating double data rate (DDR)5 DRAM as the area for profit generation. The approach distinguishes between restoring a technology-leadership image in advanced processes and clearly identifying product lines that can immediately contribute to earnings, reallocating resources accordingly. To this end, Samsung crafted a production strategy centered on server-grade DDR5 RDIMM, expanding the share of commodity DRAM. The choice reflects profitability deterioration caused by certification delays and price competition in HBM3E, with the underlying intent to reduce operating-profit volatility through high-margin products.

Price indicators support this judgment. The list price of 64GB DDR5 RDIMM surged from about $265 in the third quarter of last year to $450 in the fourth quarter, a roughly 70% increase in a single quarter. In spot markets, transactions as high as $780 have even been reported. The combination of server expansion and increased AI data center investment has tightened supply of high-capacity DDR5 modules, pushing prices higher. For Samsung Electronics, which significantly lowered average selling prices (ASP) to secure share after a delayed entry into HBM3E, the DDR5 market has become an especially attractive opportunity.

This strategic shift is being reflected in production reconfiguration. Recently, Samsung Electronics decided to sequentially convert 1a (10nm-class fourth-generation) processes—previously accounting for 30–40% of DRAM production capacity—to 1b and 1c nodes. The approximately 80,000 wafers per month secured through this transition are planned to be deployed to commodity DRAM production, including DDR5, LPDDR5X, LPDDR6, and GDDR7. The calculation is to defend earnings by expanding volumes in the persistently supply-constrained commodity DRAM market rather than accepting utilization declines stemming from HBM3E.

Enhancing platform trust and strengthening market position

Taken together, Samsung Electronics’ dual strategy can be summarized as a loss-leader approach: placing HBM4 at the forefront to preempt market trust while recouping actual profits from other product lines. A loss leader refers to sacrificing some short-term profitability to secure market trust and entry barriers through a core product, then recovering profits through subsequent or related products. Typically offered below cost or standard pricing, the product serves as a “lure,” strengthening overall brand competitiveness and selection advantage.

In the semiconductor industry, technical specifications, supply priority, and generational leadership often substitute for price cuts as the loss-leader mechanism. While HBM4 serves as the benchmark, actual profit recovery occurs in relatively mature, mass-supply-capable product lines such as DDR5. For this reason, the prevailing view in the industry is that Samsung’s decision to manage HBM4 volumes supplied to NVIDIA at the mid-20% level reflects an intent to confine its role to the minimum necessary to clearly demonstrate technological superiority.

The core of this strategy lies not in HBM4’s sales performance itself, but in the platform trust and market position it secures. Being the first HBM4 installed in next-generation AI accelerators of a key customer like NVIDIA symbolically demonstrates Samsung Electronics’ memory technology level. Once this benchmark is firmly established, bargaining power and optionality in subsequent HBM generations or large-scale supply contracts are likely to expand. With DDR5 anchoring short-term earnings and HBM4 setting mid-to-long-term technology benchmarks, each playing distinct roles, observers note that the overall portfolio’s stability could be enhanced.