Samsung Foundry faces a 2-nanometer inflection point as talks with AMD test pricing, yields, and trust

Input

Modified

Targeting a simultaneous rebound in memory and foundry

TSMC raises prices backed by near-monopoly power

Yield stability and production credibility remain key challenges

Samsung Electronics is seeking an opportunity to revive its foundry business through large-scale supply negotiations with AMD. As rival TSMC has effectively monopolized the 2-nanometer process and moved to raise prices while selectively accepting orders, Samsung is positioning itself to actively court customers that place greater emphasis on production timing and price rationality. The key issue is whether Samsung can stabilize yields and secure mass-production credibility at the 2-nanometer node, making the negotiations a critical test of whether the company can break the cycle of customer departures that has repeatedly surfaced at advanced nodes.

More than a one-off deal, a bid to secure a reference customer

According to industry sources on the 15th, Samsung’s foundry division is currently in talks with AMD to supply chips fabricated on its next-generation 2-nanometer (SF2) process. The discussions reportedly involve AMD’s next-generation server CPU, EPYC Venice, and are seen as a symbolic opportunity for Samsung to regain momentum in leading-edge manufacturing. After losing major customers to TSMC at the previous 3-nanometer node, Samsung now faces pressure to restore technological credibility and create a turning point for its foundry business.

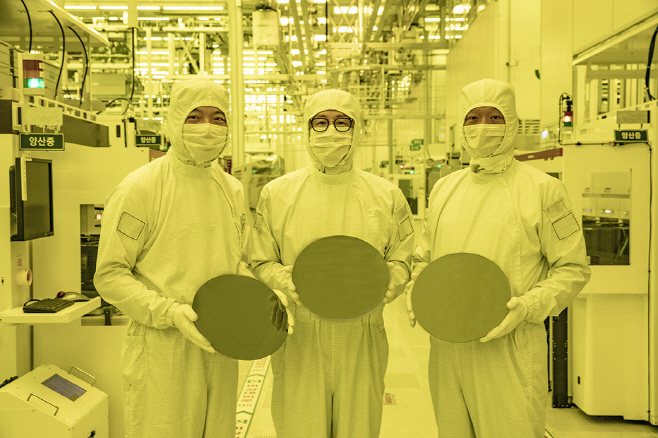

Samsung plans to produce prototype 2-nanometer chips using a multi-project wafer (MPW) approach as part of its collaboration with AMD. MPW allows multiple customer designs to be fabricated on a single wafer, reducing entry barriers during the early stages of a new process. The two companies plan to assess whether Samsung’s 2-nanometer technology meets AMD’s requirements for performance, power efficiency, and area before deciding on a final contract around January next year. Given the potentially large volumes involved if a deal is finalized, industry observers view the talks as a de facto validation of Samsung’s 2-nanometer process itself.

Securing EPYC Venice volumes would mean more than a single contract for Samsung, effectively establishing a tangible reference customer at the leading edge. In the foundry industry, yields and process stability improve through real production experience, as manufacturers absorb trial and error while handling actual customer volumes. This dynamic explains why TSMC has maintained its technological lead by processing large volumes for customers such as Apple and Nvidia over extended periods. Winning a major server CPU customer like AMD would allow Samsung to rapidly accumulate mass-production experience at 2 nanometers and provide a strong basis for persuading other technology clients.

While Samsung has regained performance momentum in memory, particularly through high-bandwidth memory (HBM), its foundry business continues to lag in global market share and customer trust. According to TrendForce, TSMC’s share of the global foundry market surpassed 70 percent for the first time in the second quarter and expanded to 71.0 percent in the third quarter. Samsung’s share stood at just 6.8 percent in the third quarter. Without extending the recovery in memory into the foundry segment, Samsung faces difficulty restoring balance across its semiconductor business.

AI-driven order backlogs tighten supply

By contrast, TSMC, which has effectively monopolized the 2-nanometer node, is leveraging its supply advantage to raise prices and screen orders, narrowing customers’ choices. According to Reuters, TSMC has set pricing for its 2-nanometer process more than 50 percent higher than the previous 3-nanometer generation. The core driver is its overwhelming market position. With near-exclusive control over sub-3-nanometer production, major technology firms are competing to secure capacity even at higher costs. This concentration of demand has placed TSMC in a position where it no longer needs to accept every order, strengthening its negotiating power.

Soaring investment costs are another factor behind the price increases. Fabricating circuits at 2 nanometers and below requires ASML’s High-NA extreme ultraviolet lithography tools, which cost more than $345 million per unit, compared with roughly $138 million for standard EUV systems. Rising design and manufacturing complexity has also driven up research and development spending and labor costs for highly skilled engineers, making price increases difficult to avoid from TSMC’s perspective.

The AI-driven expansion of order backlogs has further intensified supply bottlenecks. Taiwanese technology outlet DigiTimes reported in October that major customers such as Nvidia and MediaTek had already pre-booked most of TSMC’s 2-nanometer capacity for next year, with production lines expected to run at full utilization from mid-year. Demand for advanced packaging is also nearing saturation. These conditions further entrench TSMC’s ability to push both higher prices and selective order acceptance.

As a result, customer selection criteria are gradually shifting. Assuming performance gaps narrow to a manageable level, production timing and price rationality are emerging as more decisive factors. An industry source said that competing with TSMC inevitably requires price competitiveness, adding that Samsung’s strategy of leveraging pricing as the second-largest foundry player is a highly realistic choice. As TSMC’s capacity tightens and pricing pressure increases, Samsung Foundry may emerge as an immediately viable alternative for some customers.

All-out effort to prevent customer defections

For Samsung to turn the 2-nanometer negotiations into a genuine inflection point, it must overcome the legacy of customer losses seen during previous node transitions. Samsung previously partnered with AMD on its 4-nanometer process, but concerns over process stability were never fully resolved, and the volumes ultimately shifted to TSMC. AMD had initially planned to manufacture certain products, including server CPUs, with Samsung but overhauled its strategy late in development. The episode became a textbook example of how trust issues at advanced nodes can directly trigger strategic pivots by customers.

Customer departures were not limited to AMD. Google chose TSMC to manufacture Tensor G5 and G6 application processors for the Pixel 10 and 11 series, while Qualcomm also selected TSMC over Samsung for production of its next-generation Snapdragon 8 Elite 2 processor. A common factor behind these decisions was skepticism over Samsung Foundry’s yields and mass-production stability at advanced nodes. With TSMC’s improved 3-nanometer (N3E) yields estimated at 80 to 90 percent, customers have prioritized suppliers capable of delivering stable volumes on fixed schedules.

The problem is compounded by its financial impact. Samsung’s System LSI and foundry divisions recorded operating losses of approximately $3.6 billion last year, followed by more than $1.4 billion in losses in the first quarter alone this year, raising concerns that annual losses could exceed $4.1 billion. These accumulated losses have translated directly into reduced capital investment. During a recent earnings call, Samsung said it would prioritize converting existing lines rather than expanding new capacity, taking market conditions and investment efficiency into account. Given that competitiveness at advanced nodes is closely tied to investment scale, prolonged delays in restoring profitability and trust risk perpetuating a negative cycle.

Even so, some analysts argue that the environment surrounding the 2-nanometer node differs from previous cycles. Counterpoint Research projects Samsung’s 2-nanometer capacity will expand from about 8,000 wafers per month this year to 21,000 wafers by the end of next year, representing a 163 percent increase. With yields estimated to have improved to as much as 60 percent, Samsung is said to have secured additional orders, including a $16.5 billion contract for Tesla’s next-generation AI6 chip, along with Exynos 2600, Apple image sensors, and select application-specific integrated circuit projects.

Still, skepticism remains over whether Samsung can prevent the loss of core server CPU customers such as AMD. More important than short-term yield improvements is the ability to sustain those yields over time and demonstrate unwavering adherence to mass-production schedules. In this context, the AMD negotiations are widely viewed as a decisive test of whether Samsung Foundry can finally break the pattern of repeated defections at the leading edge, and ultimately as the most critical variable determining the success or failure of its foundry revival.